# AT73C240-EK1 Evaluation Kit

.....

# **User Guide**

## Section 1

| Introducti | on                    | 1-1 |

|------------|-----------------------|-----|

| 1.1        | Scope                 | 1-1 |

| 1.2        | AT73C240-EK1 Features | 1-2 |

| 1.3        | Deliverables          | 1-2 |

## Section 2

| Getting S | tarted     |                                                                        | 2-1    |

|-----------|------------|------------------------------------------------------------------------|--------|

| 2.1       | Electros   | tatic Warning                                                          | 2-1    |

| 2.2       | Requirer   | ments                                                                  | 2-1    |

| 2.3       | PC Syst    | em Requirements                                                        | 2-1    |

| 2.4       | Instructio | ons                                                                    | 2-2    |

|           | 2.4.1      | To start the AT73C240-EK1 board (before using the AT73C240-EK1 softwar | e) 2-2 |

|           | 2.4.2      | To turn off the AT73C240-EK1 evaluation board                          | 2-2    |

| 2.5       | Block Di   | agram                                                                  | 2-3    |

| 2.6       | Typical (  | Connection Application                                                 | 2-3    |

| 2.7       | Power S    | Supply                                                                 | 2-4    |

|           | 2.7.1      | AC/DC Transformer or External Power Supply                             | 2-4    |

|           | 2.7.2      | Supply With a Power Supply on Audio Power Amplifier                    | 2-6    |

|           | 2.7.3      | On Board Supply Voltage                                                | 2-6    |

| 2.8       | Commu      | nication Interfaces                                                    | 2-7    |

|           | 2.8.1      | Serial Interfaces Header                                               | 2-7    |

|           | 2.8.2      | SPI Setup                                                              | 2-8    |

|           | 2.8.3      | TWI Setup                                                              | 2-9    |

|           | 2.8.4      | I <sup>2</sup> S Extension Header                                      | 2-10   |

| 2.9       | Audio In   | terfaces                                                               | 2-11   |

|           | 2.9.1      | Headset 32 Ohms Output                                                 | 2-11   |

|           | 2.9.2      | Power Amplifier Output (PA)                                            | 2-11   |

| 2.10      | General    | Configuration                                                          | 2-13   |

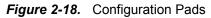

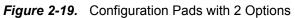

|           | 2.10.1     | Configuration Pads                                                     | 2-13   |

|           |            |                                                                        |        |

## Section 3

| Parallel-to | o-serial Card                                                          | 3-1 |

|-------------|------------------------------------------------------------------------|-----|

| 3.1         | Parallel-to-serial Card Features                                       | 3-1 |

| 3.2         | Parallel-to-serial Card Components Placement                           | 3-2 |

| 3.3         | Electrostatic Warning                                                  | 3-2 |

| 3.4         | Requirements                                                           | 3-2 |

| 3.5         | Instructions                                                           | 3-3 |

|             | 3.5.1 To start the Parallel-to-Serial card (before using any software) | 3-3 |

|             | 3.5.2 To turn off the Parallel-to-Serial card evaluation board         | 3-3 |

| 3.6         | Block Diagram                                                          | 3-4 |

| 3.7 | 7 Power Supply |                             |      |

|-----|----------------|-----------------------------|------|

|     | 3.7.1          | AC/DC Transformer           | 3-5  |

|     | 3.7.2          | Vpad Supply Option          |      |

|     | 3.7.3          | Adjustable Output Voltage   |      |

| 3.8 | Commu          | unication Interfaces        | 3-9  |

|     | 3.8.1          | Serial Interfaces Header    | 3-9  |

|     | 3.8.2          | 12.288 MHz Clock            | 3-10 |

|     | 3.8.3          | On Board Configuration Pads | 3-10 |

## Section 4

| AT73C24 | 0-EK1 Software Interface | 1-1 |

|---------|--------------------------|-----|

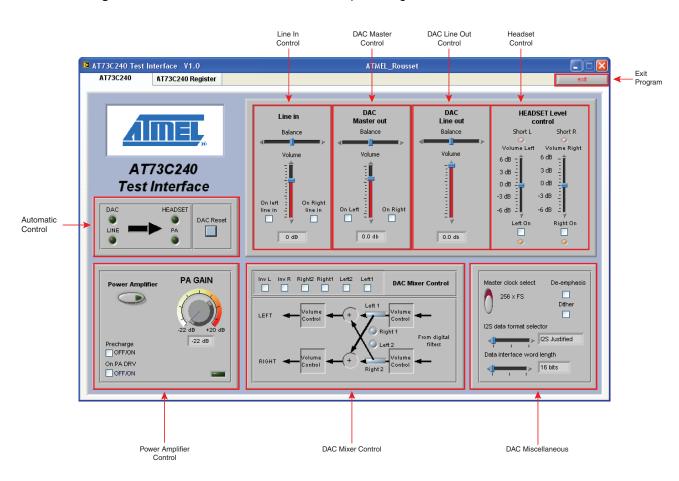

| 4.1     | Software Panel           | 4-1 |

## Section 5

| Technical | Specifications5-1       |  |

|-----------|-------------------------|--|

| 5.1       | AT73C240-EK1            |  |

| 5.2       | Parallel-to-Serial Card |  |

## Section 6

| PCB Lay | /out                    | 6-1 |

|---------|-------------------------|-----|

| 6.1     | AT73C240-EK1            | 6-1 |

| 6.2     | Parallel-to-Serial Card | 6-3 |

## Section 7

| Schematics7-1 | 1 |

|---------------|---|

|---------------|---|

## Section 8

| Revision | History          |  |

|----------|------------------|--|

| 8.1      | Revision History |  |

## Introduction

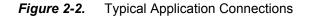

Congratulations on your purchase of the AT73C240-EK1. It is designed to give designers a quick start to evaluate the audio capability of the AT73C240 and for prototyping and testing of new designs.

#### 1.1 Scope

This document describes the AT73C240-EK1. This board is designed to allow an easy evaluation of the products using demonstration software.

To increase its capabilities for demonstration, this standalone board has two serial interfaces (Serial Peripheral Interface and I<sup>2</sup>S via a dedicated connector).

This user guide acts as a general getting started guide as well as a complete technical reference for advanced users.

This document refers the AT73C240 Datasheet.

**Typical Applications:**

- MP3-Player

- PDA, Camera, Mobile Phone

- Car Audio/Multimedia

- Home Audio/Multimedia

#### 1.2 AT73C240-EK1 Features

The AT73C240-EK1 provides the following features:

- Power supply:

- AC/DC transformer input (6V to 9V)

- or External Power Supply pad

- On-board resources:

- 20-bit stereo audio DAC,

- 90dB SNR playback stereo channels,

- 1 stereo 32 Ohm/20mW stereo headset (3.5mm jack connector),

- 1 speaker 8 Ohms output (3.5mm jack connector),

- 1 line stereo input (2 RCA)

- Serial interfaces:

- SPI (by default),

- TWI (by hardware modification),

- l<sup>2</sup>S

- On-board buttons:

- AT73C240 Reset,

- SPI/TWI Communication,

- TWI Address selection

#### 1.3 **Deliverables**

The AT73C240-EK1 package contains the following items:

- An AT73C240-EK1 board,

- A Parallel-to-Serial board,

- A DC/DC power supply cable,

- 20-Lead flat cable,

- A parallel cable,

- One CD-ROM containing the product's software, User Guide and a full Datasheet.

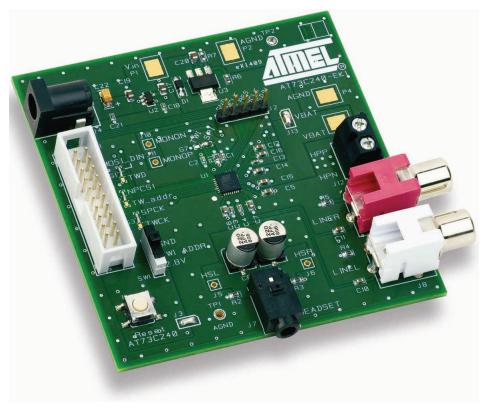

Figure 1-1. AT73C240-EK1 Top View (card photo)

The AT73C240 is located in the center of the AT73C240-EK1 on the Components Side.

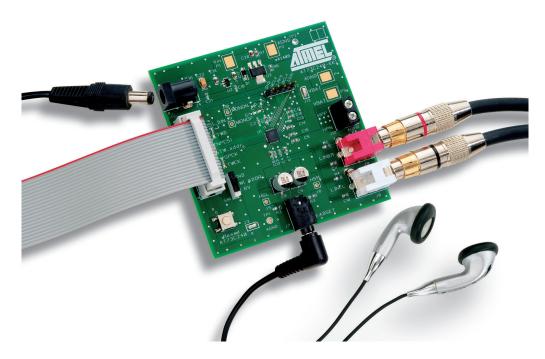

Figure 1-2. AT73C240-EK1Card With Available Connections

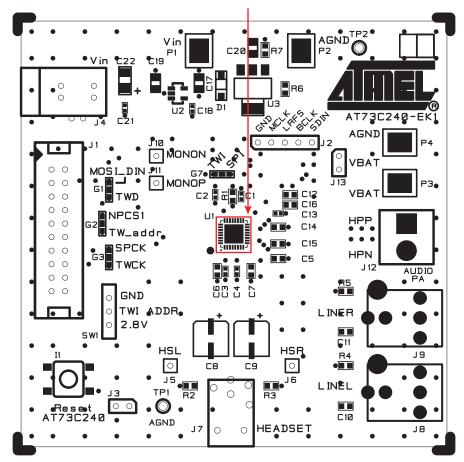

Figure 1-3. AT73C240-EK1 Components Side

## Section 2

## **Getting Started**

### 2.1 Electrostatic Warning

The AT73C240-EK1 evaluation board is shipped in protective anti-static packaging. The board must not be subjected to high electrostatic potentials. A grounding strap or similar protective device should be connected when handling the board. Avoid touching the components pins or any metallic element.

#### 2.2 Requirements

In order to set up the AT73C240-EK1 evaluation kit the following items are needed:

- 1. The AT73C240-EK1 evaluation board itself.

- 2. A DC output power source for main supply:

- Transformer 6V to 9V DC max (minimum 500 mA is required) or,

- External power supply connected to Vin pad.

- 3. A DC output power source for Power Amplifier supply:

- Transformer 3V to 5.5V DC max (minimum 300mA is required) or,

- External power supply connected to Vbat pad.

- 4. Input/Output devices (Headset, Speaker, etc)

- 5. PC station with an extension peripheral of SPI/TWI (i.e. Parallel-to-Serial board) for command communication (via micro-controller or PC) and/or an I<sup>2</sup>S extension for audio streaming.

### 2.3 PC System Requirements

For a correct software operation of the AT73C240-EK1 evaluation board, the minimum hardware and software PC requirements are:

- Intel<sup>®</sup> Pentium<sup>®</sup> II processor

- 64 MB RAM

- 70 MB free hard disk space (for AT73C240 Evaluation board software installation)

- Windows<sup>®</sup> 2000/XP/VISTA

- A parallel port.

### 2.4 Instructions

### 2.4.1 To start the AT73C240-EK1 board (before using the AT73C240-EK1 software)

- Install «DLPORTIO.exe» from the provided software CD and restart your PC.

- Install the AT73C240 software by clicking on setup.exe.

- If the software is downloaded from the Atmel Web site then it is necessary to install first the National Instrument Labview software (LabVIEW8.0.1RuntimeEngine).

- Configure the on-board jumpers as in the relevant paragraphs:

- 1. Section 2.7.3 "On Board Supply Voltage" on page 2-6

- 2. Section 2.8.2 "SPI Setup" on page 2-8

- 3. Section 2.8.3 "TWI Setup" on page 2-9

- Connect DC/DC power supply cable between AT73C240-EK1 board and Parallel-to-Serial card (Section 2.7.1 "AC/DC Transformer or External Power Supply" on page 2-4) or if used connect an external power supply on Audio Amplifier (Section 2.7.2 "Supply With a Power Supply on Audio Power Amplifier" on page 2-6)

- Connect Input and Output devices to the AT73C240-EK1 board (into linein, Headset, Power Amplifier, etc..) as in Section 2.9 "Audio Interfaces" on page 2-11,

- Connect a transformer to the Parallel-to-Serial card,

- Connect the Parallel cable to the Parallel-to-Serial card and then, connect the 20-pin flat cable between the to Parallel-to-Serial card and the AT73C240-EK1 board.

- An I<sup>2</sup>S serial interface extension (J2) is available for connecting a micro-controller directly to the AT73C240,

- Launch the AT73C240 software Test interface by clicking on AT73C240.exe

#### 2.4.2 To turn off the AT73C240-EK1 evaluation board

Disconnect the chosen power supply.

### 2.5 Block Diagram

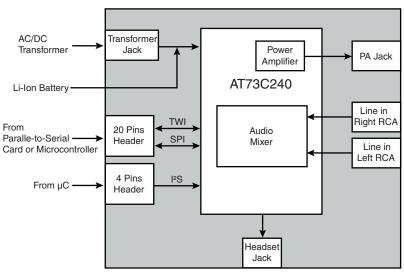

#### Figure 2-1. AT73C240-EK1 Block Diagram

## 2.6 Typical Connection Application

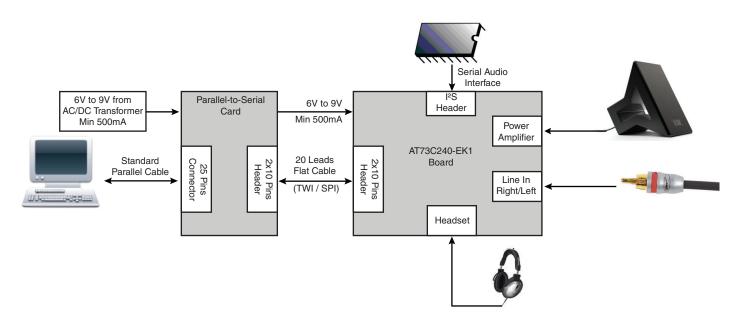

### 2.7 Power Supply

The AT73C240-EK1 is supplied with the following voltage sources:

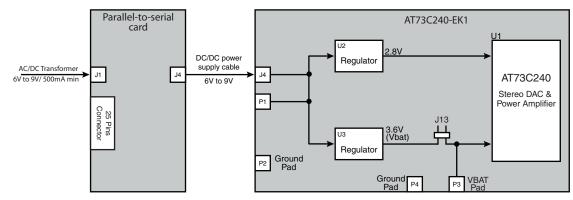

- DC/DC Power supply cable from Parallel-to-serial card (connected on J4 of Parallel-to-Serial card and on J4 of AT73C240-EK1) and,

- External Power Supply (connected on J1 of Parallel-to-Serial card) and,

- External Power Supply (connected on P3 of AT73C240-EK1);

This last power supply is not necessary if J13 is closed.

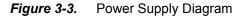

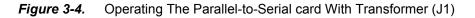

#### *Figure 2-3.* Power Supply Diagram

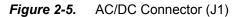

#### 2.7.1 AC/DC Transformer or External Power Supply

The transformer is used as the main power source (Vin) for the AT73C240-EK1. Connect it, to J1 of Parallel-to-serial card (NEB21R type), when using the software.

#### Table 2-1. Transformer Requirements

| Power supply source                      | Min | Мах | Unit |

|------------------------------------------|-----|-----|------|

| Transformer (minimum 500 mA is required) | 6   | 9   | V    |

The power supply voltage is regulated with on board circuitry. Input voltage on this connector should be between 6V and 9V.

Note: This power supply input is NOT protected against polarization inversion.

#### Figure 2-4. Operating The AT73C240-EK1(J4)

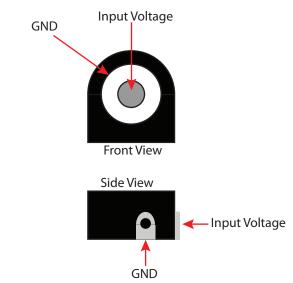

If chosen as an alternative, connect the power supply (+) to Vin pad (P1) and (-) to GND pad (P2).

#### 2.7.2 Supply With a Power Supply on Audio Power Amplifier

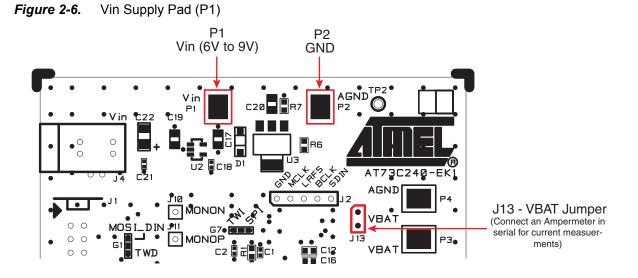

If chosen, the Audio Power Amplifier of the AT73C240 can be supply by an external supply. Connect the supply (+) to pad P3 and (-) to GND pad P4 and remove the jumper J13.

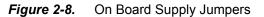

#### 2.7.3 On Board Supply Voltage

The on board supply voltage "grain-cafe" (G4, G5, & G6 located on the print-side of the board - layer 2) enable correct connection between the Power Supply and the AT73C240. Keep these jumpers closed or open them for current measurements (see Figure 2-18 on page 2-13).

### 2.8 Communication Interfaces

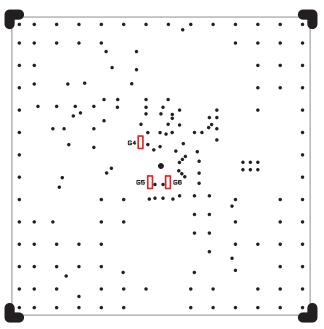

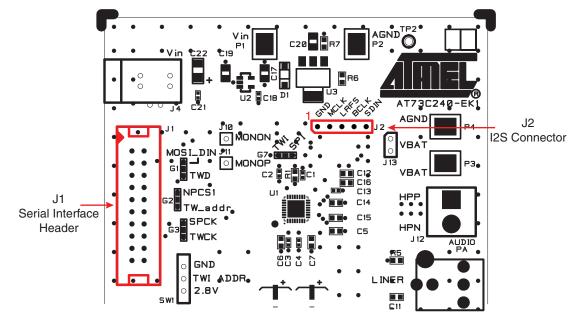

#### 2.8.1 Serial Interfaces Header

The following table details the pin assignments for each signal. In the case of not using the Parallel-to-Serial board, a serial communication (SPI or TWI) cable can drive directly by connecting it to the 2x10 pin header (J1 - Type HE10 for flat cable).

**Note:** MCLK must run during any SPI or TWI write access. In any case of <u>not using</u> the Serial Board and connecting an external communication system for SPI or TWI, a MCLK should be connected on pin 12. Otherwise, when using the Serial Board, MCLK is provided. Please consult the product Datasheet for MCLK configuration.

| Pin N° | Signal Name | Description                             | Pin N° | Signal Name   | Description              |

|--------|-------------|-----------------------------------------|--------|---------------|--------------------------|

| 1      | MOSI_DIN    | Data in                                 | 2      | -             | Not Used                 |

| 3      | SPCK        | SPI Clock                               | 4      | GND           | Ground                   |

| 5      | NPCS1       | SPI CS                                  | 6      | -             | Not Used                 |

| 7      | -           | Not Used                                | 8      | GND           | Ground                   |

| 9      | TWCK        | TWI Clock                               | 10     | 2V8           | 2.8V out                 |

| 11     | LRFS        | I <sup>2</sup> S LRFS <sup>(1)</sup>    | 12     | MCLK          | I <sup>2</sup> S M-clock |

| 13     | SDIN        | I <sup>2</sup> S Data in <sup>(1)</sup> | 14     | -             | Not Used                 |

| 15     | -           | Not Used                                | 16     | -             | Not Used                 |

| 17     | BCLK        | I <sup>2</sup> S B-clock <sup>(1)</sup> | 18     | SPI_DOUT_MISO | SPI Data out             |

| 19     | -           | Not Used                                | 20     | TWD           | TWI Data                 |

Table 2-2. Serial Interface Header Pins Assigning

*Note:* **1.** The I<sup>2</sup>S signals are independent. They are connected to the Serial Interface Header but not to the level-shifter on the Parallel-to-Serial card.

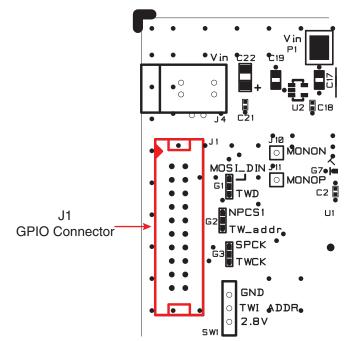

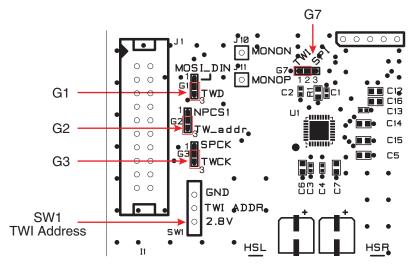

#### 2.8.2 SPI Setup

The SPI protocol is detailed in the product Datasheet.

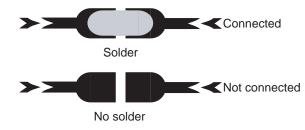

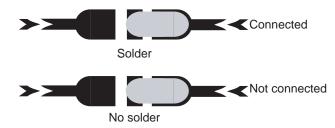

Before connecting a SPI signal to the Serial Interface Header, configure G1, G2, G3 and G7 as in the following figure (for soldering instructions see Figure 2-19 on page 2-13):

- G1, G2, G3 pads 1 and 2 are soldered

- G7 pads 2 and 3 are soldered

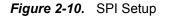

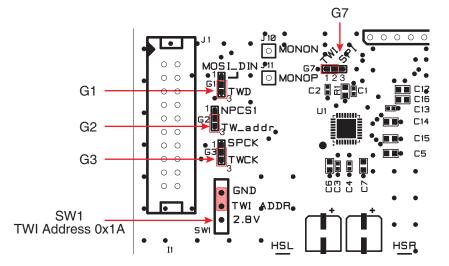

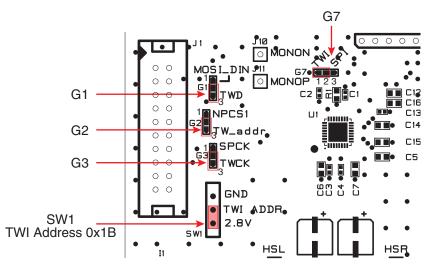

#### 2.8.3 TWI Setup

The TWI protocol is details in the product Datasheet.

Before connecting a TWI signal to the Serial Interface Header, configure G1, G2, G3, G7 and SW1 (for TWI address) as in the following figures (for soldering instructions see Figure 2-19 on page 2-13):

- SW1 is switched to the address when: GND = Address 0x1A and 2.8V = Address 0x1B,

- G1, G2, G3 pads 2 and 3 are soldered,

- G7 pads 1 and 2 are soldered.

Figure 2-12. TWI Address Switch (SW1) - Case Address = 0

Figure 2-13. TWI Address Switch (SW1) - Case Address = 1

#### 2.8.4 I<sup>2</sup>S Extension Header

An 1x5 pin header (J2) is use as an extension to directly drive the I<sup>2</sup>S interface from an external host.

Its signals are connected in Parallel-to-Serial Interface Header (J1). see Section 2-2 "Serial Interface Header Pins Assigning" on page 2-7.

- Pin N° 1 GND.

- Pin N° 2 MCLK.

- Pin N° 3 LRFS.

- Pin N° 4 BCLK.

- Pin N° 5 SDIN.

Figure 2-14. I<sup>2</sup>S Serial Header (J2)

### 2.9 Audio Interfaces

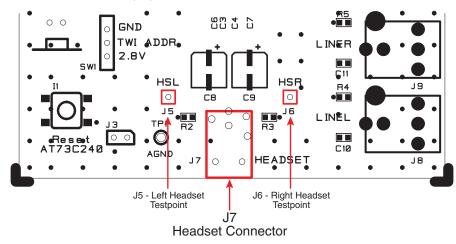

#### 2.9.1 Headset 32 Ohms Output

The Headset output is connected to a 3.5mm jack connector (J7). The positive and negative output signals can be monitored on J5 and J6.

Figure 2-15. Headset Connector (J7)

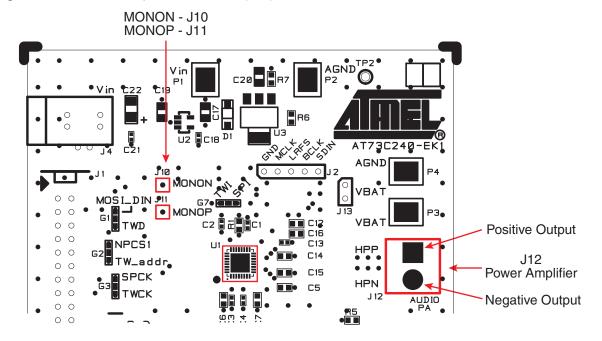

#### 2.9.2 Power Amplifier Output (PA)

The Power Amplifier output is connected to a 2-screw connector (J12). The positive output is connected to pin 1 and the negative to pin 2.

Figure 2-16. Power Amplifier Connector (J12)

**Note:** By default the MONON and MONOP outputs are looped to PAIN pins (see Figure 7-1 on page 7-1). If needed these signals can be monitored on J10 and J11.

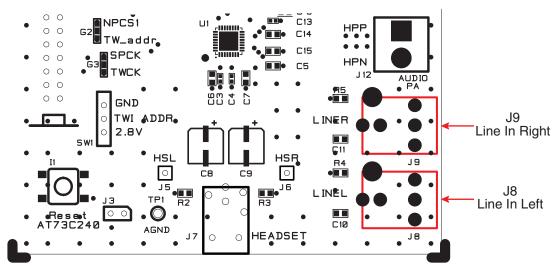

#### 2.9.2.1 Line Inputs

A line stereo signal can be sent through RCA connectors J8 (Left) and J9 (Right).

### 2.10 General Configuration

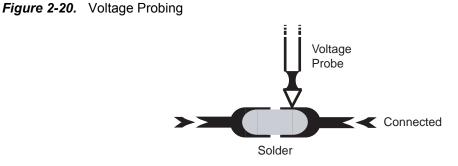

#### 2.10.1 Configuration Pads

A configuration pad configures the AT73C240-EK1 Evaluation Board for custom application. The configuration is programmable by soldering a specific part of the configuration pad. To return to the initial configuration, the customer has to solder a short jumper.

#### 2.10.1.1 Measurement Probing

Any measurement should be done with a CLOSED configuration pad.

Figure 2-21. Current Probing

## Parallel-to-serial Card

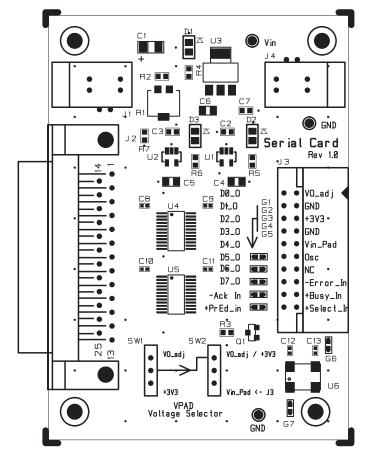

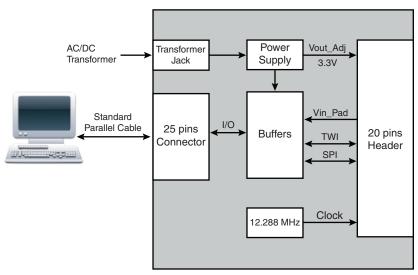

The Parallel-to-Serial card allows computer terminals to communicate with all PMAAC product line.

It gives designers all necessary for a quick setup of an extended card and it supports different product's software.

To increase its capabilities for demonstration, this standalone board has two serial interfaces (TWI and SPI).

#### 3.1 Parallel-to-serial Card Features

The Parallel-to-Serial card provides the following features:

- Power supply:

- AC/DC transformer or,

- External supply.

- On-board resources:

- Standard 25 pins Parallel interface,

- 20 leads GPIO connector,

- 12.288MHz Clock output for digital core,

- Adjustable 1.8V to 3.9V output voltage (1A max)

- Fixed 3.3V output voltage (100mA max),

- 3 power identification leds.

- Serial interfaces:

- Bidirectional buffered Parallel to SPI,

- Bidirectional buffered Parallel to TWI.

- On-board buttons:

- Vpad Selection.

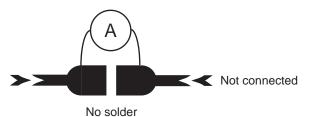

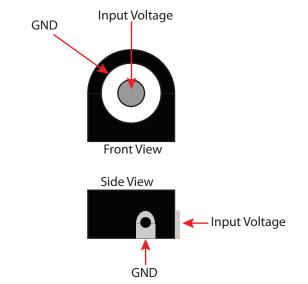

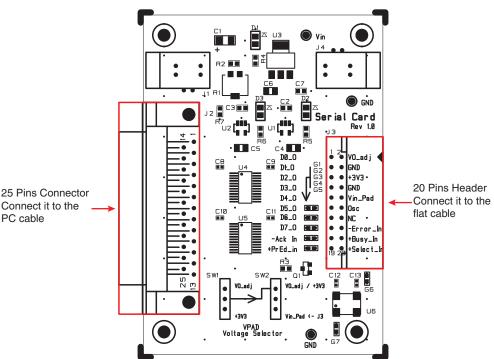

## 3.2 Parallel-to-serial Card Components Placement

#### Figure 3-1. Parallel-to-serial Card Components Placement

#### 3.3 Electrostatic Warning

The Parallel-to-Serial card evaluation board is shipped in protective anti-static packaging. The board must not be subjected to high electrostatic potentials. A grounding strap or similar protective device should be connected when handling the board. Avoid touching the components pins or any metallic element.

#### 3.4 Requirements

In order to set up the Parallel-to-Serial card the following items are needed:

- 4. The Parallel-to-Serial card itself.

- 5. An output DC power source:

- Transformer 6V to 9V DC max (minimum 500 mA is required) or,

- External power supply connected to Vin pad.

- 6. PC station with a 25 pins parallel connector.

### 3.5 Instructions

### 3.5.1 To start the Parallel-to-Serial card (before using any software)

- Configure the on-board switches and trimmer as in the relevant paragraphs:

- 1. Section 3.7.2 "Vpad Supply Option" on page 3-7

- 2. Section 3.7.3 "Adjustable Output Voltage" on page 3-8

- 3. Section 3.8.2 "12.288 MHz Clock" on page 3-10

- 4. Section 3.8.3 "On Board Configuration Pads" on page 3-10

- 5. Section 2.10 "General Configuration" on page 2-13

- Connect a transformer to the Parallel-to-Serial card (Section 3.7.1 "AC/DC Transformer" on page 3-5),

- Connect the Parallel cable to the Parallel-to-Serial card and then,

- Connect the 20-pins flat cable between the to Parallel-to-Serial card and the evaluation board.

- Once the Serial Communication Card properly installed; it should operate transparently as if it were a standard cable connection. Operating power supplied directly from the AC/DC transformer; there is no ON/OFF switch. All data signals from and to the PC are passed straight through.

#### 3.5.2 To turn off the Parallel-to-Serial card evaluation board

Disconnect the chosen power supply.

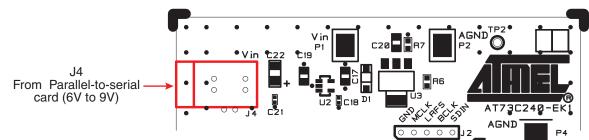

### 3.6 Block Diagram

#### Figure 3-2. Parallel-to-Serial Card Block Diagram

## 3.7 Power Supply

The Parallel-to-Serial card is supplied with the following voltage sources:

- AC/DC Transformer (connected on J1) or,

- External Power Supply (connected on TP1 and GND)

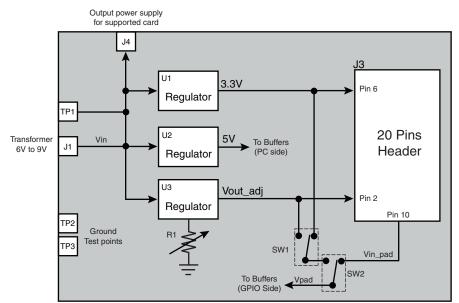

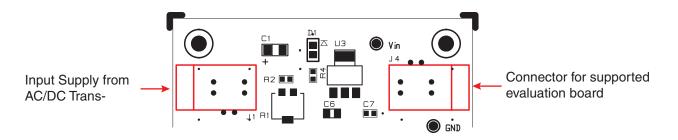

#### 3.7.1 AC/DC Transformer

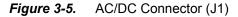

The transformer is used as the main power source (AC/DC) for the Parallel-to-Serial card. Connect it, to J1 (NEB21R type), before using any software.

| Table 3-1. | Transformer | Requirements |

|------------|-------------|--------------|

|------------|-------------|--------------|

| Power supply source                      | Min | Мах | Unit |

|------------------------------------------|-----|-----|------|

| Transformer (minimum 500 mA is required) | 6   | 9   | V    |

The power supply voltage is regulated with on board circuitry. Input voltage on this connector should be included between 6V and 9V.

It can supply-power a supported card trough J4 connector which enables to use only the main AC/DC Transformer (connected on J1). Use the two-side male 2.1mm cable to connect power-supply between the two card (see Figure 3-4 on page 3-35).

Note: This power supply input is NOT protected against polarization inversion.

If chosen as an alternative, connect the power supply (+) to Vin test-point (TP1) and (-) to GND tsetpoint(TP2 or TP3).

Figure 3-6. Vin Supply Test-Points

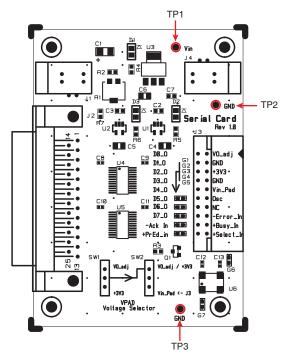

On the Parallel-to-Serial card 3 leds indicate voltage present:

- D1 Adjustable Output Voltage

- D2 +3.3V

- D3 +5V

The Vpad is the supply voltage for the buffers for the extension card side. It is the choice of the user to determinate Vpad functionality and there are 3 option:

- 1. Supply by Vin\_Pad from an extension card (pin 10 on J3).

- 2. Supply by 3.3V from on board 3.3V LDO (U2)

- 3. Supply by adjustable voltage from on board adjustable Regulator (U3); see "Adjustable Output Voltage" on page 3-8

Please consult the following 3 figures for Vpad supply available options.

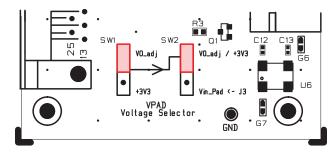

Figure 3-8. Vpad Supplied By Vin\_Pad

SW2 is in Vin\_Pad position. SW1 has no effect.

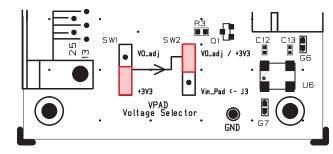

Figure 3-9. Vpad Supplied By On Board 3.3V

SW2 is in VO\_adj/+3V3 position. SW1 is in +3V3 position.

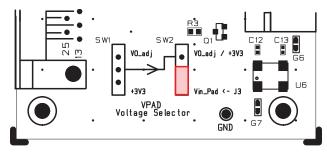

#### Figure 3-10. Vpad Supplied By Board Adjustable Voltage

SW2 is in VO\_adj/+3V3 position. SW1 is in VO\_adj position.

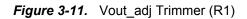

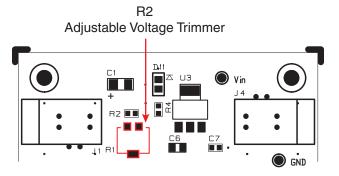

#### 3.7.3 Adjustable Output Voltage

The Parallel-to-Serial card is able to supply up to 1A adjustable output voltage (Vout\_adj = 1.8V to 3.9V) for powering an extended card. Vout\_adj output level is trimmed by R1 and Its output pin is located on pin N° 2 on J3 header.

### 3.8 Communication Interfaces

#### 3.8.1 Serial Interfaces Header

The Parallel-to-Serial card supports both SPI and TWI protocols which configured automatically by the software. The following table details the pins assigning for each signal on J3 (2x10 pins header - Type HE10 for flat cable).

*Note:* In most cases, a clock must run during any SPI or TWI write access. In any case of <u>not using</u> the Serial Board and connecting an external communication system for SPI or TWI a clock should be provided to the supported evaluation card.

| Pin N° | Signal Name  | Description                | Pin N° | Signal Name  | Description                                       |

|--------|--------------|----------------------------|--------|--------------|---------------------------------------------------|

| 1      | Data0_Out    | Output Data <sup>(1)</sup> | 2      | Vout_adj     | Adjustable Output Voltage (1A max) <sup>(4)</sup> |

| 3      | Data1_Out    | Output Data <sup>(1)</sup> | 4      | GND          | Ground <sup>(3)</sup>                             |

| 5      | Data2_Out    | Output Data <sup>(1)</sup> | 6      | +3V3         | Output voltage<br>(100mA max)                     |

| 7      | Data3_Out    | Output Data <sup>(1)</sup> | 8      | GND          | Ground <sup>(3)</sup>                             |

| 9      | Data4_Out    | Output Data <sup>(1)</sup> | 10     | Vin_pad      | Input supply from<br>supported card               |

| 11     | Data5_Out    | Output Data <sup>(1)</sup> | 12     | OSC          | 12.288MHz Output clock for supported digital core |

| 13     | Data6_Out    | Output Data <sup>(1)</sup> | 14     | NC           | Not Connected                                     |

| 15     | Data7_Out    | Output Data <sup>(1)</sup> | 16     | -Error_in    | Input Data <sup>(2)</sup>                         |

| 17     | -Ack_in      | Input Data <sup>(2)</sup>  | 18     | +Busy_in     | Input Data <sup>(2)</sup>                         |

| 19     | +PaperEnd_in | Input Data <sup>(2)</sup>  | 20     | +SelectIn_in | Input Data <sup>(2)</sup>                         |

Table 3-2. Serial Interface Header Pins Assigning

*Notes: 1.* Output Data - An output signal from parallel port to supported card.

- 2. Input Data An input signal from supported card to parallel port.

- **3.** Ground These pins must be connected between the Parallel-to-Serial card and the supported board.

- 4. Output current is determinate by the limitation of the ACDC transformer.

Figure 3-12. Serial Interfaces Connectors (J2 & J3)

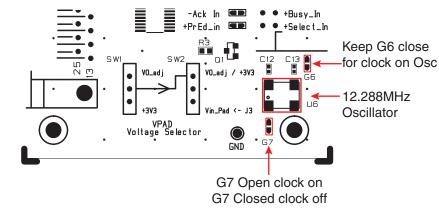

#### 3.8.2 12.288 MHz Clock

The Parallel-to-Serial card's oscillator (X1) provides 12.288MHz clock (+3.3V p-p). This clock is necessary for driving the digital core of the evaluated board - via pin 12 on J3.

G6 connect the oscillator output clock with pin 12 on J3. Open it if clock is not necessary.

Keep G7 enables/disable the oscillator. If open then clock is "ON". If closed then clock is "OFF".

#### 3.8.3 On Board Configuration Pads

The "Grain-cafe" G1 to G5 are **not soldered** by default. Simply solder it if these signal should be connected to the buffers.

## AT73C240-EK1 Software Interface

### 4.1 Software Panel

Figure 4-1. Software Panel - General Purpose Page

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | (Mu                                                                                                                                                                                          | TWI/SPI<br>Selector<br>ust be setup<br>ore startup)                                | Read<br>Command                                                                             | Write<br>Command                                             | i i                                                                                            | Write<br>Content                                                                      | Read<br>Content                                                                      |                                                                                        | gister<br>dress                                                                                       |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                               | AT73C240 Test Inte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rface V1.0<br>T73C240 Register                                                                                                                                                               |                                                                                    |                                                                                             | A                                                            | TMEL_Rousse                                                                                    | et 🛛                                                                                  |                                                                                      |                                                                                        | exit                                                                                                  |

| Automatic Readegister Mapping |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Read<br>ofFion                                                                                                                                                                               | Input interfac<br>communicati<br>TVI -<br>SPI -<br>Y<br>TVI Address<br>0x1B -<br>y | n                                                                                           | Write<br>Read                                                | _                                                                                              | 240 7<br>ite content                                                                  | rest Int                                                                             |                                                                                        | ddress                                                                                                |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Register Name                                                                                                                                                                                | Bit7                                                                               | Bit6                                                                                        | Bit5                                                         | Bit4                                                                                           | Bit3                                                                                  | Bit2                                                                                 | Bit1                                                                                   | BitO                                                                                                  |

|                               | 0x00 DAC Contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                            |                                                                                    | ONPADRV                                                                                     |                                                              | ONDACL                                                                                         | ONLNOR                                                                                |                                                                                      |                                                                                        | DICO                                                                                                  |

|                               | 0x00 DAG CONT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                            | 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.                                           | ONPADRO                                                                                     | ONDACR                                                       | ONDACL                                                                                         | ONLINOK                                                                               | ONLNOL                                                                               | ONLNIR                                                                                 | ONLNIL                                                                                                |

|                               | 0x01 DAC Left Li                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                              |                                                                                    | -                                                                                           | ONDACR                                                       | LLIG                                                                                           | LLIG                                                                                  | ONLNOL                                                                               | ONLNIR<br>LLIG                                                                         |                                                                                                       |

|                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ne In Gain                                                                                                                                                                                   |                                                                                    |                                                                                             |                                                              |                                                                                                |                                                                                       |                                                                                      |                                                                                        | ONLNIL                                                                                                |

|                               | 0x01 DAC Left Li<br>0x02 DAC Right L<br>0x03 DAC Left M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ne In Gain<br>ine In Gain<br>aster Playback Gain                                                                                                                                             | -                                                                                  | -                                                                                           | -<br>LMPG                                                    | LLIG<br>RLIG<br>LMPG                                                                           | LLIG<br>RLIG<br>LMPG                                                                  | LLIG<br>RLIG<br>LMPG                                                                 | LLIG<br>RLIG<br>LMPG                                                                   | ONLNIL<br>LLIG<br>RLIG<br>LMPG                                                                        |

|                               | 0x01 DAC Left Li<br>0x02 DAC Right L<br>0x03 DAC Left M<br>0x04 DAC Right M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ne In Gain<br>ine In Gain<br>aster Playback Gain<br>flaster Playback Gain                                                                                                                    | -<br>-<br>-                                                                        | -<br>-<br>-<br>-                                                                            | -<br>LMPG<br>RMPG                                            | LLIG<br>RLIG<br>LMPG<br>RMPG                                                                   | LLIG<br>RLIG<br>LMPG<br>RMPG                                                          | LLIG<br>RLIG<br>LMPG<br>RMPG                                                         | LLIG<br>RLIG<br>LMPG<br>RMPG                                                           | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG                                                                |

|                               | 0x01 DAC Left Li<br>0x02 DAC Right L<br>0x03 DAC Left M<br>0x04 DAC Right N<br>0x05 DAC Left Li                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ne In Gain<br>ine In Gain<br>aster Playback Gain<br>flaster Playback Gain<br>ne Out Gain                                                                                                     |                                                                                    | -<br>-<br>-<br>-                                                                            | -<br>LMPG<br>RMPG<br>LLOG                                    | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG                                                           | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG                                                  | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG                                                 | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG                                                   | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG                                                        |

|                               | 0x01         DAC Left Li           0x02         DAC Right L           0x03         DAC Left M           0x04         DAC Right L           0x05         DAC Left Li           0x06         DAC Right L                                                                                                                                                                                                                                                                                                                                                                                           | ne In Gain<br>ine In Gain<br>aster Playback Gain<br>flaster Playback Gain<br>ne Out Gain<br>ine Out Gain                                                                                     |                                                                                    | -<br>-<br>-<br>-<br>-                                                                       | -<br>LMPG<br>RMPG<br>LLOG<br>RLOG                            | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG                                                   | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG                                          | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG                                         | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG                                           | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG                                                |

|                               | 0x01 DAC Left Li<br>0x02 DAC Right L<br>0x03 DAC Left M<br>0x04 DAC Right L<br>0x05 DAC Left M<br>0x05 DAC Left Li<br>0x06 DAC Right L<br>0x07 DAC Output                                                                                                                                                                                                                                                                                                                                                                                                                                        | ne In Gain<br>ine In Gain<br>aster Playback Gain<br>Master Playback Gain<br>ne Out Gain<br>ine Out Gain<br>Level Control                                                                     | RSHORT                                                                             | -<br>-<br>-<br>-<br>-<br>-<br>ROLC                                                          | -<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC                    | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC                                           | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LSHORT                                | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC                                         | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC                                   | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC                                        |

|                               | 0x01         DAC Left Li           0x02         DAC Right Li           0x03         DAC Left M           0x04         DAC Right Li           0x05         DAC Left M           0x06         DAC Right Li           0x06         DAC Right Li           0x06         DAC Right Li           0x07         DAC Night Li           0x08         DAC Night Li                                                                                                                                                                                                                                         | ne In Gain<br>Ine In Gain<br>aster Playback Gain<br>daster Playback Gain<br>ne Out Gain<br>Level Control<br>Control<br>Control                                                               |                                                                                    | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | -<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVR            | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>RLOG<br>ROLC<br>INVL                                   | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LSHORT<br>RMSMIN2                             | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC<br>RMSMIN1                              | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LMSMIN2                        | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LMSMIN1                             |

|                               | 0x01         DAC Left Li           0x02         DAC Right Li           0x03         DAC Left M           0x04         DAC Right Li           0x05         DAC Right Li           0x06         DAC Right Li           0x07         DAC Cotput           0x08         DAC Output           0x08         DAC Might Li           0x08         DAC Cock -                                                                                                                                                                                                                                             | ne In Gain<br>ine In Gain<br>aster Playback Gain<br>daster Playback Gain<br>ne Out Gain<br>ine Out Gain<br>Level Control<br>Control<br>3. Sampling Frequency Control                         | RSHORT                                                                             | -<br>-<br>-<br>-<br>-<br>ROLC<br>-                                                          | -<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVR            | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVL<br>OVRSEL                         | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LSHORT<br>RMSMIN2                             | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC<br>RMSMIN1                              | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LM5MIN2                        | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LMSMIN1                             |

|                               | 0x01         DAC Left Li           0x02         DAC Right Li           0x03         DAC Left Min           0x04         DAC Left Li           0x05         DAC Left Li           0x07         DAC Output           0x08         DAC Mixer           0x08         DAC Mixer           0x09         DAC Colock           0x00A         DAC Mixer                                                                                                                                                                                                                                                   | ne In Gain<br>Ine In Gain<br>Sater Playback Gain<br>faster Playback Gain<br>ne Out Gain<br>Level Control<br>Level Control<br>3 Sampling Frequency Control<br>I aneous                        |                                                                                    | -<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | -<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVR            | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVL<br>OVRSEL<br>DINTSEL              | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LSHORT<br>RMSMIN2<br>DITHEN                   | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC<br>RMSMIN1<br>DEEMPEN                   | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LMSMIN2<br>-<br>NBITS          | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>LMPG<br>LLOG<br>RLOG<br>LOC<br>LMSMINI<br>-<br>NBITS                |

|                               | 0x01         DAC Left Li           0x02         DAC Right Li           0x03         DAC Left M           0x04         DAC Right Li           0x05         DAC Right Li           0x06         DAC Right Li           0x07         DAC Chight Li           0x08         DAC Right Li           0x08         DAC Night Li           0x08         DAC Night Li           0x08         DAC Chick I                                                                                                                                                                                                   | ne In Gain<br>Ine In Gain<br>Sater Playback Gain<br>faster Playback Gain<br>ne Out Gain<br>Level Control<br>Level Control<br>3 Sampling Frequency Control<br>I aneous                        |                                                                                    |                                                                                             | LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVR<br>DINTSEL      | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVL<br>OVRSEL                         | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LSHORT<br>RMSMIN2                             | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC<br>RMSMIN1                              | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LM5MIN2                        | ONLNIL<br>LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LMSMIN1                             |

|                               | 0x01         DAC Left Li           0x02         DAC Right Li           0x03         DAC Left M           0x04         DAC Right Li           0x05         DAC Left M           0x06         DAC Right Li           0x06         DAC Right Li           0x06         DAC Right Li           0x07         DAC Color Mixer           0x08         DAC Right Li           0x09         DAC Color Mixer           0x00         DAC Right Li                                                                                                                                                           | ne In Gain<br>Ine In Gain<br>Sater Playback Gain<br>4aster Playback Gain<br>ne Out Gain<br>Ine Out Gain<br>Level Control<br>Control<br>Sampling Frequency Control<br>Ianeous<br>arge Control |                                                                                    | ROLC<br>VCMCAPSEL                                                                           | LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVR<br>DINTSEL      | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVL<br>OVRSEL<br>DINTSEL<br>PRCHGPDRV | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LSHORT<br>RMSMIN2<br>-<br>DITHEN<br>PRCHGLNIR | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC<br>RMSMINI<br>-<br>DEEMPEN<br>PRCHGLNIL | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>RLOG<br>LOLC<br>LMSMIN2<br>-<br>NBITS<br>PRCHG | ONLINIL<br>LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LLOLC<br>LMSTINI<br>NBITS<br>ONMSTR                |

|                               | 0x01         DAC Left Li           0x02         DAC Right Li           0x03         DAC Left Ministry           0x04         DAC Right Ministry           0x05         DAC Right Ministry           0x06         DAC Right Ministry           0x06         DAC Right Ministry           0x07         DAC Output           0x08         DAC Right Ministry           0x08         DAC Ministry           0x08         DAC Clock           0x00         DAC Right Ministry           0x00         DAC Ministry           0x00         DAC Right Ministry           0x01         DAC Right Ministry | ne In Gain<br>Ine In Gain<br>Sater Playback Gain<br>4aster Playback Gain<br>ne Out Gain<br>Ine Out Gain<br>Level Control<br>Control<br>Sampling Frequency Control<br>Ianeous<br>arge Control |                                                                                    | -<br>-<br>-<br>ROLC<br>-<br>-<br>VCMCAPSEL<br>-                                             | LMPG<br>RMPG<br>LLOG<br>RLOG<br>ROLC<br>INVR<br>-<br>DINTSEL | LLIG<br>RLIG<br>LMPG<br>RMPG<br>LLOG<br>ROLC<br>INVL<br>OVRSEL<br>DINTSEL<br>PRCHEDRV          | LLIG<br>RLIG<br>RMPG<br>LLOG<br>RLOG<br>LSHORT<br>RMSMIN2<br>DITHEN<br>PRCHGLNIR      | LLIG<br>RLIG<br>LMPG<br>LLOG<br>RLOG<br>LOLC<br>RMSMIN1<br>DEEMPEN<br>PRCHGLNIL      | LLIG<br>RLIG<br>LMPG<br>LLOG<br>LLOG<br>LOLC<br>LMSMIN2<br>NBITS<br>PRCHG<br>RESFILZ   | ONLINIL<br>LLIG<br>RLIG<br>LMPG<br>LLOG<br>LLOG<br>LOLC<br>LOLC<br>LMSMINI<br>NBITS<br>ONMSTR<br>RSTZ |

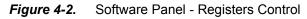

- *Note:* Resetting all the registers done by pressing once on the AT73C240 Reset push-button I2. In the next read action the registers will be at their default values.

- Figure 4-3. Reset AT73C240 Button

## Section 5

# **Technical Specifications**

## 5.1 AT73C240-EK1

| System Unit: AT73C240-EK1                                                          |                        |

|------------------------------------------------------------------------------------|------------------------|

| <ul> <li>Physical Dimensions</li> <li>Weight</li> </ul>                            |                        |

| <ul> <li>Operating Conditions</li> </ul>                                           |                        |

| <ul> <li>External Voltage Supply (From AC/DC Transformer or on Vin Pad)</li> </ul> | <b>6V - 9V</b> /500 mA |

| <ul> <li>External Voltage Supply (on VBAT Pad)</li> </ul>                          | 3V - 5.5V              |

| Connections                                                                        |                        |

| - Communication Connector                                                          | 2x10 pins Header       |

| <ul> <li>– I<sup>2</sup>S Serial Connector</li> </ul>                              | 1x5 pins Header        |

## 5.2 Parallel-to-Serial Card

| System Unit: Parallel-to-Serial card                                 |                        |

|----------------------------------------------------------------------|------------------------|

| <ul> <li>Physical Dimensions</li> <li>Weight</li> </ul>              |                        |

| <ul> <li>Operating Conditions</li> </ul>                             |                        |

| <ul> <li>External Voltage Supply (From AC/DC Transformer)</li> </ul> | <b>6V - 9V</b> /500 mA |

| Connections                                                          |                        |

| - Communication Connector                                            | 2x10 pins Header       |

## **Section 6**

# **PCB** Layout

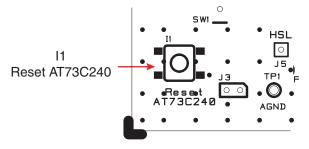

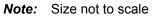

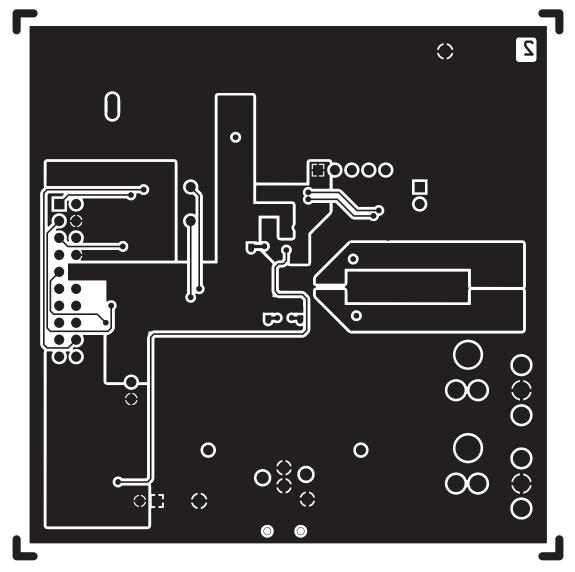

## 6.1 AT73C240-EK1

*Note:* Size not to scale

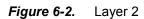

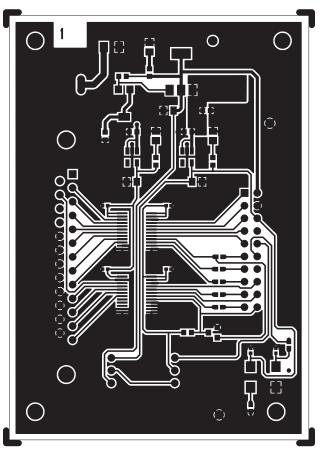

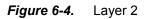

## 6.2 Parallel-to-Serial Card

Figure 6-3. Layer 1 - Components Layer

*Note:* Size not to scale

*Note:* Size not to scale

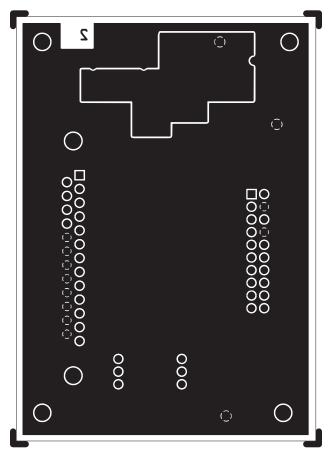

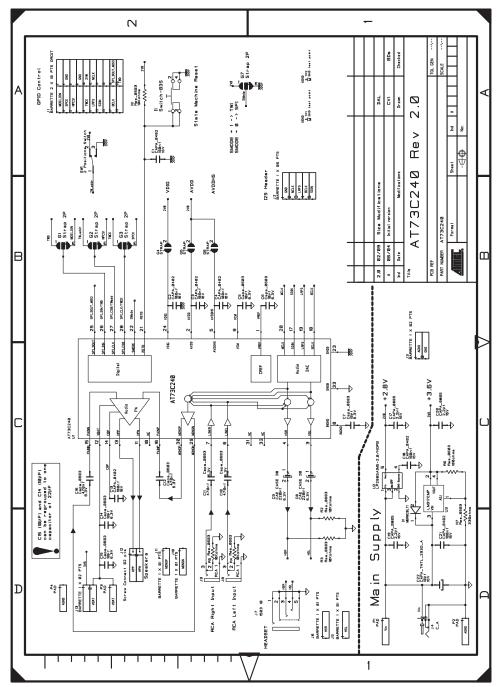

## **Schematics**

Figure 7-1. AT73C240-EK1 Schematic

Figure 7-2. Parallel-to-Serial Card Schematic

## Section 8

## **Revision History**

## 8.1 Revision History

### Table 8-1. Revision History

| Document | Comments                 | Change Request Ref. |

|----------|--------------------------|---------------------|

| 6482A    | First Issue, 15-May-2009 |                     |

#### Headquarters

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

#### Web Site

www.atmel.com www.atmel.com/products/powermanage/default.asp *Technical Support* Atmel techincal support Sales Contacts www.atmel.com/contacts/

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, or warranted for use as components in applications intended to support or sustain life.

© 2009 Atmel Corporation. All rights reserved. Atmel®, Atmel logo and others are registered trademarks of Atmel Corporation or its subsidiaries. Windows® and others are registered trademarks or trademarks of Microsoft Corporation in the US and/or other countries. Other terms and product names may be the trademarks of others.